Contact us. We'll get back to you within 24 hours

You might like

-

K9 ASIC Multifunctional Tester – Hashboard & PSU Diagnostic Tool$205.90 USD$205.90 USD $299.00 USDSale Sold out

-

Gen2 ASIC Miner Blower Silencer – Noise Reduction for Antminer, Whatsminer, Avalon, Iceriver$68.00 USD$68.00 USDSale Sold out

-

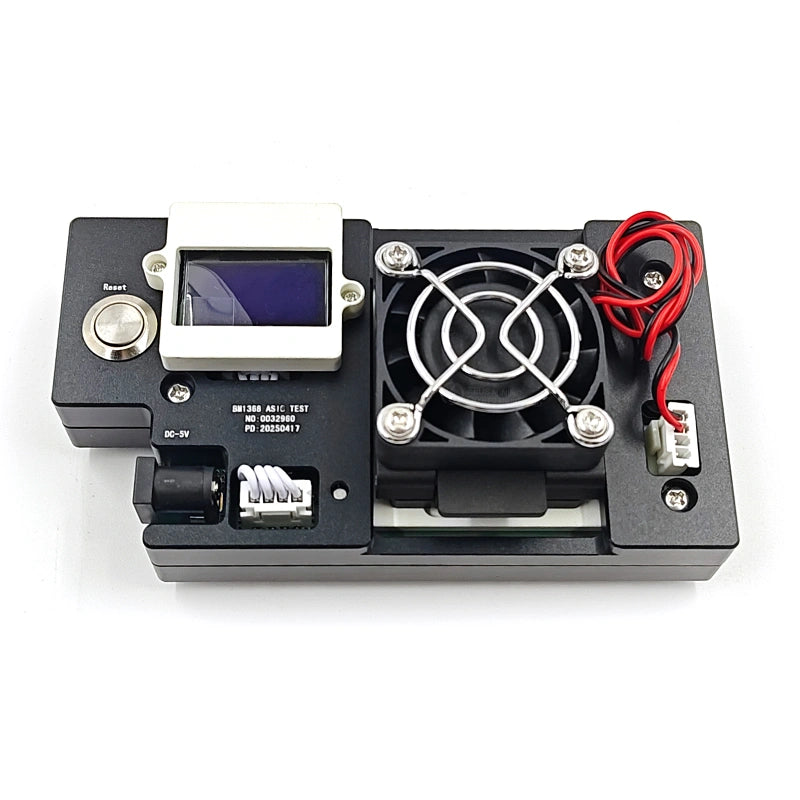

BM1368 BM1368PB BM1368AA BM1368PA BM1368PV Series ASIC Chip Tester for Antminer S21XP S21 T21 Hash Boards Crypto Miner Repair$314.90 USD$314.90 USD $365.00 USDSale Sold out

-

Whatsminer CB6 V10 Control Board Replacement for M20s M21s M30s M30 M31s+ M32 M50$36.00 USD$36.00 USD $44.90 USDSale Sold out

Shopping cart (0)

You might like

- Choosing a selection results in a full page refresh.

- Opens in a new window.